# INSTITUTO POLITÉCNICO NACIONAL CENTRO DE INVESTIGACIÓN EN COMPUTACIÓN

### Lagarto:

Una estrategia para la Generación, Aplicación y Transferencia de conocimiento para el Desarrollo de la Industria de las TIC en México

### CONTENIDO

- Introducción

- Lagarto: El primer procesador mexicano

- Objetivos

- ¿Qué se requiere para integrarse al proyecto?

- ¿Qué ofrece el IPN?

- Plan de generación de conocimiento

- Fases de desarrollo:

- Fase 1: Arquitectura y Sistema Operativo

- Fase 2: Multinúcleos y Redes de Interconexión

- · Fase 3: Creación de un ecosistema

- Conclusiones

Lagarto es un proyecto en desarrollo para generar conocimiento en dos áreas principales.

- Diseño de Arquitecturas de procesadores

- Técnicas de alto rendimiento

- Técnicas de bajo consumo de energía

- Sistemas operativos (Linux)

- Adecuación a la arquitectura Lagarto

- Metodología para el desarrollo de drivers

- Consolidar grupos de Investigación, Desarrollo e innovación (I+D+i) en áreas de:

- Diseño de procesadores

- Diseño Digital (HDL-FPGA's)

- Diseño de Sistemas Operativos (Linux)

en instituciones de educación con nivel de posgrado, superior y media superior de todo el país, con la ayuda de los CEC del IPN.

- Que se utilice como material educativo.

- Reducir la dependencia de conocimiento y la dependencia tecnológica.

- Que se convierta en un estándar para la industria Mexicana de las TIC

### ¿Qué se requiere para que te integres al proyecto?

- Formación de grupos de académicos

- Arquitectura de computadoras

- Diseño Digital (HDL-FPGA)

- Sistemas Operativos

- Supercómputo para la innovación

- Plataformas de desarrollo FPGA's (Altera, Xilinx)

- Cluster de GPUs

### ¿Qué ofrece la red de Computación del IPN?

- Acompañamiento de un grupo de expertos.

- Documentación

- Material para clases

- Código fuente (HDL-Verilog)

- Herramientas

- Un foro de consulta y ayuda permanente

Los CEC-IPN coordinarán la realización de talleres de entrenamiento en las áreas mencionadas.

#### Plan de Generación de Conocimiento en TIC

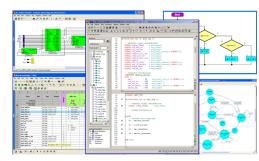

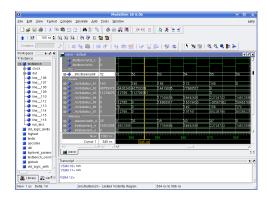

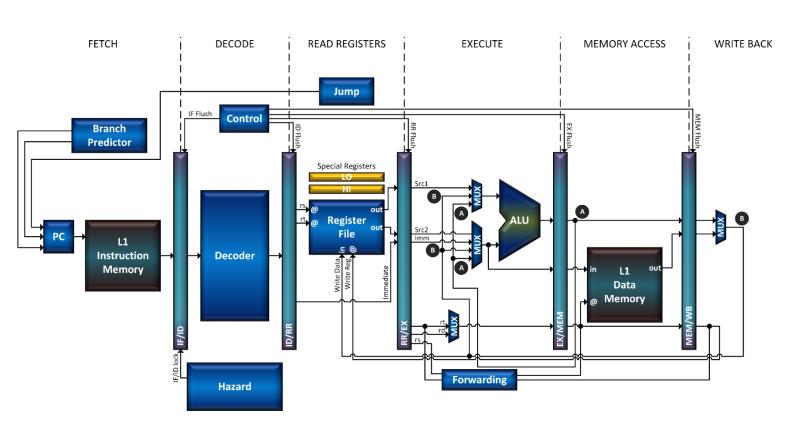

- Parte I: Incluye todo el código Verilog del núcleo de un procesador escalar con planificación dinámica, ejecución en orden, predicción dinámica de saltos y utilerías.

- Parte II: Incluye la adecuación de un Sistema Operativo Embebido (Linux), la metodología para el desarrollo de drivers, utilerías y un tutorial de instalación para plataformas de desarrollo basados en FPGA's.

Parte III: simulación de problemas complejos capaces de ejecutarse de forma eficiente en supercomputadoras modernas de bajo costo para la aplicación específica, es decir soluciones que no requieran grandes inversiones en equipo e instalaciones.

- Parte IV: Desarrollo de material educativo para universidades, Simuladores, Libros.

- Las herramientas (recomendamos) pueden ser utilizadas en investigación y docencia en las áreas de: Arquitectura de computadoras, Sistemas Operativos Embebidos, Diseño digital y Programación paralela.

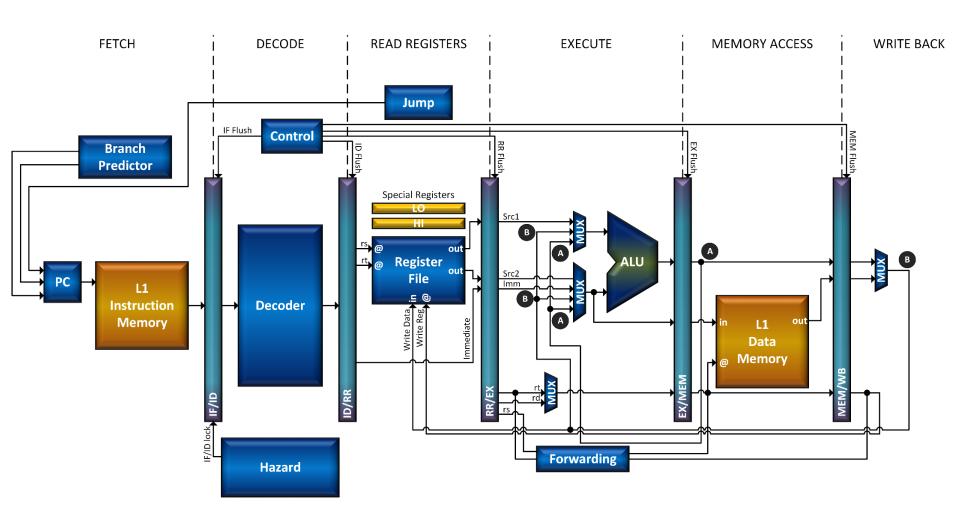

- Fase I: (2012-2016) Investigación clave para el desarrollo de las TIC:

- Arquitectura Lagarto I 32-bits, el primer procesador mexicano.

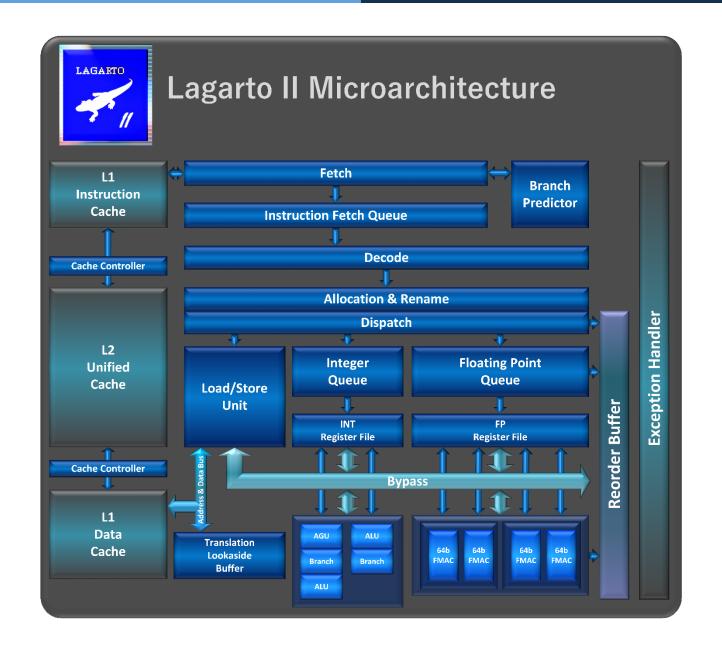

- Arquitectura **Lagarto II** 64-bits, emite 2-instrucciones, planificación dinámica y ejecución fuera de orden.

- Sistemas Operativos Linux (ESCOM)

- Diseño de PCB's para tarjetas de desarrollo (ESCOM)

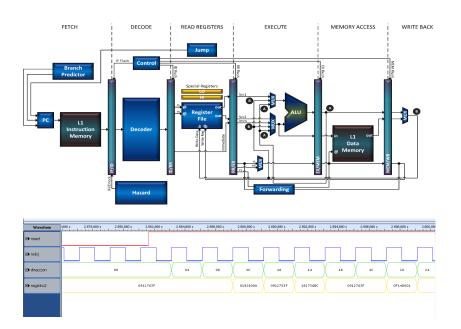

Procesador escalar segmentado (utiliza técnicas planificación dinámica modernas) con S.O. Linux.

Pruebas realizadas a Lagarto I

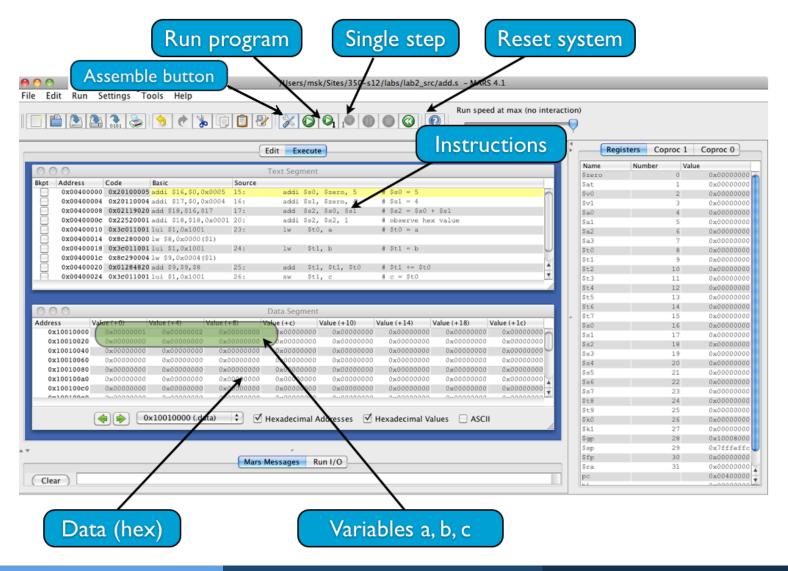

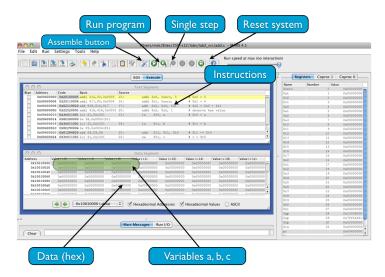

MARS (MIPS Assembler and Runtime Simulator)

http://courses.missouristate.edu/KenVollmar/MARS/

Desarrollado por Pete Sanderson (psanderson@otterbein.edu) y Kenneth Vollmar (kenvollmar@missouristate.edu)

### MARS (MIPS Assembler and Runtime Simulator)

### MARS (MIPS Assembler and Runtime Simulator)

.text .data

### Linux para arquitecturas MIPS

## **Buildroot**

### Making Embedded Linux Easy

Buildroot is a simple, efficient and easy-to-use tool to generate embedded Linux systems through cross-compilation.

http://buildroot.uclibc.org/

http://wiki.qemu.org/Main\_Page

```

🕽 🗐 🔳 ralc88@Ubuntu-CIC: ~/Escritorio/BuildRoot/MIPSI

Welcome to MIPSI

buildroot login: root

EXT2-fs (hda): error: ext2_lookup: deleted inode referenced: 363

EXT2-fs (hda): error: remounting filesystem read-only

# cat /proc/cpuinfo

EXT2-fs (hda): error: ext2_lookup: deleted inode referenced: 363

EXT2-fs (hda): error: remounting filesystem read-only

system type

: MIPS Malta

: Unknown

machine

processor

cpu model

: MIPS 24Kc V0.0 FPU V0.0

BogoMIPS

: 910.13

wait instruction

: yes

microsecond timers

: yes

tlb entries

: 16

extra interrupt vector : yes

hardware watchpoint

: yes, count: 1, address/irw mask: [0x0ff8]

isa

: mips1 mips2 mips32r1 mips32r2

ASEs implemented

: mips16

shadow register sets

: 1

kscratch registers

: 0

соге

: 0

VCED exceptions

: not available

VCEI exceptions

🐧 not available

```

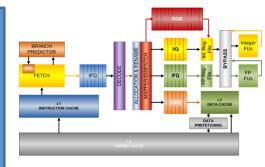

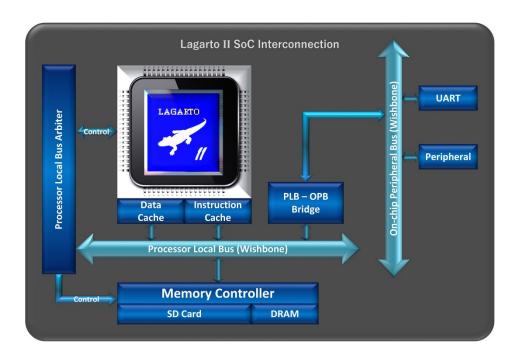

# Lagarto II

Arquitectura desarrollada por el grupo de HPCA del CIC-IPN .

Tesis de Doctorado:

"Superscalar Out of Order Processor for Embedded Systems"

César A. Hernández Calderón

Arquitectura súper-escalar

Fetch, Decode y Dispatch de hasta dos instrucciones cada ciclo de reloj.

Técnicas de planificación dinámica

Branch Predictor de dos niveles

Renombrado de Registros

Ejecución fuera de Orden

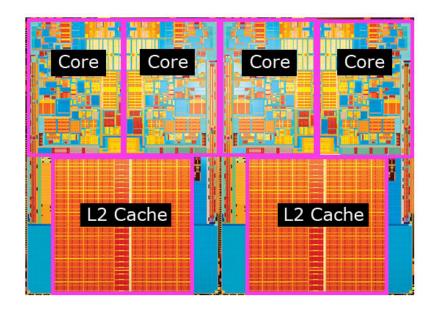

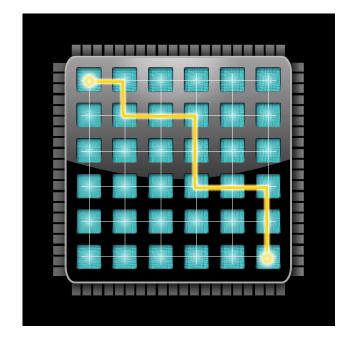

Fase II: (2017-2020)

- Productos de Investigación:

- Dual Core *Lagarto I* 32-bits.

- Quad Core Lagarto II 64-bits.

### Fase II: (2017-2020)

- Productos de Investigación:

- Redes de interconexión

Fase II

### Fase II: (2017-2020)

- Productos de Investigación:

- Fabricación de tarjetas de desarrollo (ESCOM)

### Fase III: (2020 - en adelante)

- Aplicaciones:

- Crear un ecosistema para soportar la industria Mexicana de las TIC's.

- Iniciar aplicaciones en áreas como Seguridad nacional, Educación, e-gobierno, etc.

### **Cursos próximos a realizarse:**

- Diseño y fabricación de Tarjetas de Circuito Impreso

- Programación Lenguaje Máquina (Ensamblador MIPS)

- Diseño de Circuitos Digitales (Verilog-FPGA)

- Diseño de procesadores

- Sistemas Embebidos

Centro de Investigación en Computación Prof. Marco A. Ramírez Salinas mars@cic.ipn.mx

Escuela Superior de Cómputo Prof. Jesús Yaljá Montiel Pérez yalja@ipn.mx

Escuela Superior de Ingeniería Mecánica y Eléctrica Unidad Culhuacan Prof. Juan Carlos Sánchez jcsanche@ipn.mx

Unidad Profesional Interdisciplinaria en Ingeniería y Tecnologías Avanzadas Prof. Arodi Rafael Carvallo Dominguez acarvallo@ipn.mx

Centro de Investogacion y Desarrollo de Tecnología Digital Prof. Juan José Tapia Armenta jjtapia@citedi.mx